# 具有±70V 总线故障保护、信号增强功能(SIC) 和待机模式的 CAN FD 收发器

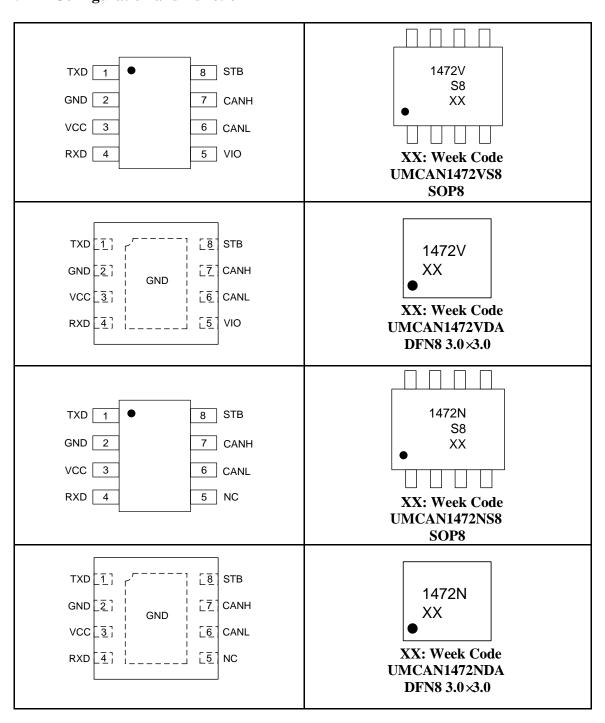

UMCAN1472VS8 SOP8 UMCAN1472NS8 SOP8 UMCAN1472VDA DFN8 3.0 ×3.0 UMCAN1472NDA DFN8 3.0 ×3.0

#### 1 描述

UMCAN1472 是高速 CAN 收发器,可在控制器局域网(CAN)协议控制器和物理双线式 CAN 总线之间提供接口。该收发器专用于汽车业的高速 CAN 应用,可以为(微控制器中的) CAN 协议控制器提供发送和接收差分信号的功能。

UMCAN1472改进了电磁兼容性 (EMC)和静电放电 (ESD)性能,并具有以下特点:

- ±70V 总线故障保护

- 电源关闭时, CAN总线具有良好的无源性能

- 具有总线唤醒功能的超低电流待机模式

- 即使不使用共模扼流圈,也具有出色的电磁兼容 (EMC) 性能

- 带有Vio管脚的型号可直接连接电源电压为3.3V和5V的微控制器

UMCAN1472 实现了 ISO 11898-2:2024 和 SAE J2284-1 至 SAE J2284-5 中定义 CAN 物理层,并与高速经典 CAN 和 CAN FD 收发器完全兼容。UMCAN1472 具备符合 ISO 11898-2:2024 参数集 C 的定义的信号改善功能(SIC)。CAN 信号改善功能可显著减少网络中的信号振铃现象,从而使 CAN FD 通信能够在更大规模的拓扑结构中可靠运行。此外,UMCAN1472 还具备更严格的位时序对称性性能,可支持最高 8 Mbit/s 的 CAN FD 通信。这些特性使UMCAN1472 成为所有类型 HS-CAN 网络的理想选择,特别适用于需要通过总线实现唤醒功能的待机模式节点。

#### 2 应用

- 汽车工业中的高速 CAN 应用

- 基础设施和农业设备

- 电梯

- 联网的传感器/执行器

#### 3 特性

- 完全符合ISO 11898-2:2024、SAE J2284-1至 SAE J2284-5和SAE J1939-14标准

- 保护特性:

- 总线故障保护: ±70V

- ±9kV IEC 61000-4-2 接触放电

- 超低电流待机模式,具有本地和总线唤醒功能

- 具备信号改善功能 (SIC)

- 低电磁辐射(EME)和高电磁抗扰度(EMI), 符合拟议的EMC标准IEC 62228-3和SAE J2962-2标准

- 数据传输速率高达 8Mbps

### **4 Ordering Information**

| Part Number  | Marking Code | Package Type | Shipping Qty               |

|--------------|--------------|--------------|----------------------------|

| UMCAN1472VS8 | 1472VS8      | SOP8         | 3000pcs/13Inch Tape & Reel |

| UMCAN1472VDA | 1472V        | DFN8 3.0×3.0 | 3000pcs/13Inch Tape & Reel |

| UMCAN1472NS8 | 1472NS8      | SOP8         | 3000pcs/13Inch Tape & Reel |

| UMCAN1472NDA | 1472N        | DFN8 3.0×3.0 | 3000pcs/13Inch Tape & Reel |

### **5 Pin Configuration and Function**

### **5 Pin Configuration and Function (continued)**

Table 5-1. Pin Functions

| Pin<br>Number | Symbol          | Description                                                                   |

|---------------|-----------------|-------------------------------------------------------------------------------|

| 1             | TXD             | Transmit data input                                                           |

| 2             | GND             | Ground (Note 1)                                                               |

| 3             | $V_{cc}$        | Supply voltage                                                                |

| 4             | RXD             | Receive data output; reads out data from the bus lines                        |

|               | NC              | Not connected in UMCAN1472NS8 and UMCAN1472NDA version                        |

| 5             | V <sub>IO</sub> | Supply voltage for I/O level adapter in UMCAN1472VS8 and UMCAN1472VDA version |

| 6             | CANL            | Low-level CAN bus line                                                        |

| 7             | CANH            | High-level CAN bus line                                                       |

| 8             | STB             | Standby mode control input                                                    |

Note 1: DFN8 package die supply ground is connected to both the GND pin and the exposed center pad. The GND pin must be soldered to board ground. For enhanced thermal and electrical performance, it is recommended that the exposed center pad also be soldered to board ground.

#### **6 Specifications**

### **6.1 Recommended Operating Conditions**

| Symbol   | Parameter                        | Conditions | Min | Тур | Max | Unit |

|----------|----------------------------------|------------|-----|-----|-----|------|

| $V_{CC}$ | Bus supply voltage               |            | 4.5 |     | 5.5 | V    |

| $V_{IO}$ | Supply voltage I/O level shifter |            | 2.9 |     | 5.5 | V    |

| $T_A$    | Operating ambient temperature    |            | -40 |     | 125 | °C   |

#### 6.2 Absolute Maximum Ratings (Note 1, 2, 3)

| Symbol             | Parameter                            | Conditions | Min  | Тур        | Max                  | Unit |

|--------------------|--------------------------------------|------------|------|------------|----------------------|------|

| $V_{CC}$           | Bus supply voltage                   |            | -0.3 |            | +7                   | V    |

| $V_{IO}$           | Supply voltage I/O level shifter     |            | -0.3 |            | +7                   | V    |

| $V_{\mathrm{BUS}}$ | Voltage range on CANH,<br>CANL       |            | -70  |            | +70                  | V    |

| $V_{\mathrm{DIF}}$ | Voltage range between CANH and CANL  |            | -40  |            | +40                  | V    |

| 17                 | Voltage range on STB                 | Note 4     | -0.3 |            | V <sub>IO</sub> +0.3 | V    |

| $V_{I}$            | Voltage range on TXD                 | Note 4     | -0.3 |            | V <sub>IO</sub> +0.3 | V    |

| Vo                 | Voltage range on RXD                 | Note 4     | -0.3 |            | V <sub>IO</sub> +0.3 | V    |

|                    |                                      | pulse 1    | -100 |            |                      | V    |

| <b>3</b> 7         | Transient voltage on CANH,           | pulse 2a   |      |            | +75                  | V    |

| $V_{trt}$          | CANL pins (Note 5)                   | pulse 3a   | -150 |            |                      | V    |

|                    |                                      | pulse 3b   |      |            | +100                 | V    |

|                    | Human body model (HBM),              | All pins   |      | <u>±</u> 8 |                      | kV   |

| $V_{\mathrm{ESD}}$ | per ANSI/ESDA/JEDEC<br>JS-001        | Other pins |      | ±4         |                      | kV   |

|                    | Contact discharge, per IEC 61000-4-2 | Bus pins   |      | ±9         |                      | kV   |

| $I_{LU}$           | Latch up, per JEDEC<br>JESD78F.01    |            |      | 200        |                      | mA   |

| $T_{VJ}$           | Virtual junction temperature         |            | -40  |            | 150                  | °C   |

| $T_{STG}$          | Storage temperature                  |            | -55  |            | 150                  | °C   |

Note 1: Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

Note 2: All voltage values, except differential I/O bus voltages, are with respect to ground terminal.

Note 3:  $V_{IO} = V_{CC}$  in non-VIO product variants.

Note 4: Maximum voltage should never exceed 7 V.

Note 5: Verified by an external test house according to IEC TS 62228, Section 4.2.4; parameters for standard pulses defined in ISO 7637.

### 6.3 Electrical Characteristics (Static) (Note 1)

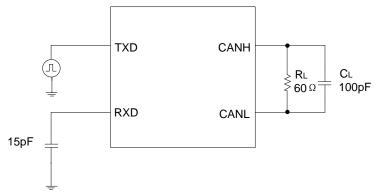

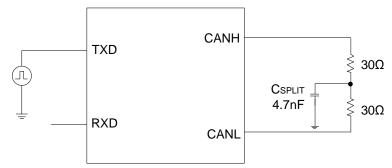

$T_J = -40$ °C to +150°C;  $V_{CC} = 4.5 \text{V}$  to 5.5 V;  $V_{IO} = 2.9 \text{V}$  to 5.5 V;  $R_L = 60 \Omega$ ;  $C_L = 100 \text{pF}$  unless otherwise specified; All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                      | Parameter                                                     | Conditions                                                                            | Min         | Тур  | Max                  | Unit |

|-----------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------|------|----------------------|------|

| Supply; pin VC              | CC                                                            |                                                                                       |             |      |                      |      |

| V <sub>UVD(STB)</sub>       | Standby undervoltage detection voltage on pin VCC             |                                                                                       | 3           | 3.6  | 4.3                  | V    |

| V <sub>UVD(SWOFF)</sub> VCC | Switch-off<br>undervoltage<br>detection voltage on<br>pin VCC | Variants without VIO                                                                  | 1.3         | 1.6  | 2.5                  | V    |

|                             |                                                               | Variants without a VIO pin; $STB = V_{CC}$ ; $TXD = V_{CC}$                           |             | 10   | 17.5                 | uA   |

|                             |                                                               | Variants with a VIO<br>pin; STB = V <sub>IO</sub> ; TXD<br>= V <sub>IO</sub>          |             | 0.4  | 1                    | uA   |

| $I_{CC}$                    | Supply current                                                | $STB = 0 V; TXD = V_{IO}$                                                             |             | 2.6  | 5                    | mA   |

|                             |                                                               | STB = 0 V; TXD = 0                                                                    | 20          | 40   | 60                   | mA   |

|                             |                                                               | STB = 0 V; TXD = 0<br>V; short circuit on bus<br>lines;<br>-3V < (CANH=CANL)<br>< 18V | 2           | 73   | 110                  | mA   |

| I/O level adapt             | er supply; pin VIO                                            |                                                                                       |             |      |                      |      |

| V <sub>UVD(SWOFF)</sub> VIO | Switch-off<br>undervoltage<br>detection voltage on<br>pin VIO | Variants with a VIO pin                                                               | 1.3         | 1.6  | 2.5                  | V    |

|                             | 1                                                             | $STB = V_{IO}; TXD = V_{IO}$                                                          |             | 8.5  | 16.5                 | uA   |

| $I_{IO}$                    | supply current on pin VIO                                     | $STB = 0 V; TXD = V_{IO}$                                                             | 5           | 10.3 | 30                   | uA   |

|                             |                                                               | STB = 0 V; TXD = 0V                                                                   |             | 72   | 300                  | uA   |

| Standby mode                | control input; pin STB                                        | T                                                                                     | 1           |      |                      |      |

| $V_{IH}$                    | High-level input voltage                                      |                                                                                       | $0.7V_{IO}$ |      |                      | V    |

| $V_{\rm IL}$                | Low-level input voltage                                       |                                                                                       |             |      | $0.3V_{\mathrm{IO}}$ | V    |

| I <sub>IH</sub>             | High-level input current                                      | $STB = V_{IO}$                                                                        | -1          |      | 1                    | uA   |

| $I_{IL}$                    | Low-level input current                                       | STB = 0 V                                                                             | -15         |      | -1                   | uA   |

### 6.3 Electrical Characteristics (Static)---continued (Note 1)

$T_J = -40$ °C to +150°C;  $V_{CC} = 4.5 \text{V}$  to 5.5 V;  $V_{IO} = 2.9 \text{V}$  to 5.5 V;  $R_L = 60 \Omega$ ;  $C_L = 100 \text{pF}$  unless otherwise specified; All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol               | Parameter                            | Conditions                                                                                                                                             | Min                  | Тур | Max                  | Unit |  |  |  |

|----------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|----------------------|------|--|--|--|

| CAN transm           | CAN transmit data input; pin TXD     |                                                                                                                                                        |                      |     |                      |      |  |  |  |

| $V_{IH}$             | High-level input voltage             |                                                                                                                                                        | $0.7V_{\mathrm{IO}}$ |     |                      | V    |  |  |  |

| $V_{\rm IL}$         | Low-level input voltage              |                                                                                                                                                        |                      |     | $0.3V_{\mathrm{IO}}$ | V    |  |  |  |

| $I_{IH}$             | High-level input current             | $TXD = V_{IO}$                                                                                                                                         | -5                   |     | 5                    | uA   |  |  |  |

| $I_{IL}$             | Low-level input current              | TXD = 0 V                                                                                                                                              | -270                 | -61 | -30                  | uA   |  |  |  |

| $C_{I}$              | Input capacitance                    |                                                                                                                                                        |                      | 5   | 10                   | pF   |  |  |  |

| CAN receive          | data output; pin RXD                 |                                                                                                                                                        |                      |     |                      |      |  |  |  |

| Іон                  | High-level output current            | $RXD = V_{IO} - 0.4 V$                                                                                                                                 | -9                   | -3  | -1                   | mA   |  |  |  |

| $I_{OL}$             | Low-level output current             | RXD = 0.4V                                                                                                                                             | 1                    | 3   | 12                   | mA   |  |  |  |

| Driver               |                                      |                                                                                                                                                        |                      |     |                      |      |  |  |  |

|                      | Dominant output                      | $\begin{split} STB &= 0 \text{ V; } TXD = 0 \text{ V;} \\ t &< t_{TO(DOM)TXD}; \\ 50  \Omega \leq R_L \leq 65  \Omega; \\ \text{pin CANH} \end{split}$ | 2.75                 | 3.5 | 4.5                  | V    |  |  |  |

| V <sub>O(DOM)</sub>  | voltage                              | $\begin{split} STB &= 0 \text{ V; } TXD = 0 \text{ V;} \\ t &< t_{TO(DOM)TXD}; \\ 50  \Omega \leq R_L \leq 65  \Omega; \\ \text{pin CANL} \end{split}$ | 0.5                  | 1.5 | 2.25                 | V    |  |  |  |

|                      |                                      | $\begin{aligned} STB &= 0 \text{ V; } TXD = 0 \text{ V;} \\ t &< t_{TO(DOM)TXD}; \\ 50  \Omega \leq R_L \leq 65  \Omega \end{aligned}$                 | 1.5                  |     | 3                    | V    |  |  |  |

| V <sub>OD(DOM)</sub> | Dominant differential output voltage | $STB = 0 \text{ V; } TXD = 0 \text{ V;}$ $t < t_{TO(DOM)TXD};$ $45 \Omega \le R_L \le 70 \Omega$                                                       | 1.4                  |     | 3.3                  | V    |  |  |  |

|                      |                                      | $STB = 0 \text{ V}; TXD = 0 \text{ V}; \\ t < t_{TO(DOM)TXD}; \\ R_L = 2240 \Omega$                                                                    | 1.5                  |     | 5                    | V    |  |  |  |

### 6.3 Electrical Characteristics (Static)---continued (Note 1)

$T_J = -40$ °C to +150°C;  $V_{CC} = 4.5 \text{V}$  to 5.5 V;  $V_{IO} = 2.9 \text{V}$  to 5.5 V;  $R_L = 60 \Omega$ ;  $C_L = 100 \text{pF}$  unless otherwise specified; All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                | Parameter                                                                   | Conditions                                                                                                           | Min                | Тур                | Max                | Unit |

|-----------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| V <sub>SYM(DOM)</sub> | Dominant output voltage symmetry, V <sub>CC</sub> - CANH – CANL             | $\begin{aligned} STB &= 0 \text{ V; } TXD = 0 \text{ V;} \\ t &< t_{TO(DOM)TXD}; \\ R_L &= 60  \Omega \end{aligned}$ | -400               |                    | 400                | mV   |

| V <sub>O(REC)</sub>   | Recessive output voltage                                                    | $\begin{aligned} STB &= 0 \text{ V; } TXD = V_{IO}; \\ R_L &= \text{open} \end{aligned}$                             | 2                  | 0.5V <sub>CC</sub> | 3                  | V    |

| V <sub>OD(REC)</sub>  | Recessive differential output voltage                                       | $STB = 0 V; TXD = V_{IO};$<br>$R_L = open$                                                                           | -50                |                    | 50                 | mV   |

| $V_{O(STB)} \\$       | Bus output voltage,<br>Standby Mode                                         | $\begin{aligned} STB &= V_{IO}; \ TXD &= V_{IO}; \\ R_L &= open \end{aligned}$                                       | -100               |                    | 100                | mV   |

| V <sub>OD(STB)</sub>  | Bus differential output<br>voltage, Standby<br>Mode                         | $STB = V_{IO}; TXD = V_{IO};$ $R_{L} = open$                                                                         | -200               |                    | 200                | mV   |

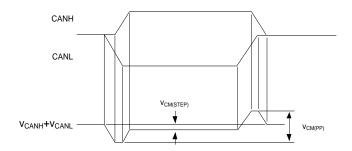

| V <sub>SYM(TX)</sub>  | Transmitter output<br>voltage symmetry,<br>(CANH +<br>CANL)/V <sub>CC</sub> | $STB = 0 \text{ V; } TXD = 250$ kHz, 1 MHz, 2.5MHz; R <sub>L</sub> = 60 $\Omega$ ; C <sub>SPLIT</sub> = 4.7 nF       | 0.9V <sub>CC</sub> |                    | 1.1V <sub>CC</sub> | V    |

| $I_{OS(DOM)}$         | Dominant short-circuit output                                               | STB = 0 V; TXD = 0 V;<br>VCC = 5 V; CANH = -15<br>V to 40 V; CANL = open                                             | -100               | -70                |                    | mA   |

| 1OS(DOM)              | current                                                                     | STB = 0 V; TXD = 0 V<br>VCC = 5 V; CANL = -15<br>V to 40 V; CANH = open                                              |                    | 70                 | 100                | mA   |

| I <sub>OS(REC)</sub>  | Recessive short-circuit output current                                      | $STB = 0 V; TXD = V_{IO};$ $-27 V \le CANH = CANL$ $\le 32 V$                                                        | -5                 |                    | 5                  | mA   |

| Receiver              |                                                                             |                                                                                                                      |                    |                    |                    |      |

| $V_{TH}$              | Differential receiver<br>threshold voltage,<br>Normal mode                  | STB = 0 V; -20 V ≤<br>CANH, CANL ≤ 20 V                                                                              | 0.5                |                    | 0.9                | V    |

| $V_{\text{ID(DOM)}}$  | Receiver dominant voltage, Normal mode                                      |                                                                                                                      |                    |                    | 9                  | V    |

| $V_{\text{ID(REC)}}$  | Receiver recessive voltage, Normal mode                                     | STB = 0 V; -20 V ≤<br>CANH, CANL ≤ 20 V                                                                              | -4                 |                    | 0.5                | V    |

| $V_{\mathrm{HYS}}$    | Differential receiver<br>hysteresis voltage,<br>Normal mode                 | STB = 0 V; -20 V ≤<br>CANH, CANL ≤ 20 V                                                                              | 50                 |                    | 300                | mV   |

### 6.3 Electrical Characteristics (Static)---continued (Note 1)

$T_J$  = -40°C to +150°C;  $V_{CC}$  = 4.5V to 5.5V;  $V_{IO}$  = 2.9V to 5.5V;  $R_L$  = 60 $\Omega$ ;  $C_L$  = 100pF unless otherwise specified; All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                  | Parameter                                                                                  | Conditions                                                                                                                             | Min  | Тур | Max  | Unit |

|-------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>TH(STB)</sub>    | Differential receiver<br>threshold voltage,<br>Standby mode                                | $\begin{split} STB &= V_{IO}; \text{-}20 \text{ V} \leq \\ CANH, \text{CANL} &\leq 20 \text{ V} \end{split}$                           | 0.4  |     | 1.15 | V    |

| V <sub>ID(DOM)STB</sub> | Receiver dominant voltage, Standby mode                                                    | $\begin{split} STB &= V_{IO}; \mbox{-}20 \ V \leq \\ CANH, \mbox{CANL} &\leq 20 \ V \end{split}$                                       | 1.15 |     | 9    | V    |

| V <sub>ID(REC)STB</sub> | Receiver recessive voltage, Standby mode                                                   | $STB = V_{IO}; -20 \text{ V} \leq \\ CANH, CANL \leq 20 \text{ V}$                                                                     | -4   |     | 0.4  | V    |

| I <sub>LKG(PD)</sub>    | Unpowered Leakage current                                                                  | $V_{CC} = V_{IO} = 0 \text{ V or}$<br>shorted to GND via 47<br>$k\Omega$ ;<br>CANH = CANL = 5  V                                       | -5   |     | 5    | uA   |

| R <sub>I</sub>          | Input resistance                                                                           | $\begin{aligned} STB &= 0 \text{ V; TXD} = V_{IO}; \\ -2 \text{ V} &\leq CANH, CANL} \\ &\leq 7 \text{ V} \end{aligned}$               | 15   | 30  | 40   | kΩ   |

| $\Delta R_{\rm I}$      | Input resistance deviation, [1 – (R <sub>IN(CANH)</sub> / R <sub>IN(CANL)</sub> )] × 100 % | $STB = 0 \text{ V; } TXD = V_{IO};$ $-2 \text{ V} \leq CANH, CANL} \leq 7 \text{ V}$                                                   | -3   |     | 3    | %    |

| R <sub>ID</sub>         | Differential input resistance                                                              | $\begin{aligned} &STB = 0 \text{ V}; \text{ TXD} = V_{IO}; \\ &-2 \text{ V} \leq \text{CANH, CANL} \\ &\leq 7 \text{ V} \end{aligned}$ | 30   | 60  | 80   | kΩ   |

| C <sub>IN</sub>         | Common-mode input capacitance to ground                                                    |                                                                                                                                        |      |     | 20   | pF   |

| C <sub>ID</sub>         | Differential input capacitance                                                             |                                                                                                                                        |      |     | 10   | pF   |

| Thermal Pro             | otection                                                                                   |                                                                                                                                        |      |     |      |      |

| T <sub>J(SD)</sub>      | Thermal shutdown threshold                                                                 | Temperature rising                                                                                                                     |      | 185 |      | °C   |

Note 1:  $V_{IO} = V_{CC}$  in non-VIO product variants.

### 6.4 Electrical Characteristics (Dynamic) (Note 7)

$T_J$  = -40°C to +150°C;  $V_{CC}$  = 4.5V to 5.5V;  $V_{IO}$  = 2.9V to 5.5V;  $R_L$  = 60 $\Omega$ ;  $C_L$  = 100pF unless otherwise specified; all voltages are defined with respect to ground.

| Symbol                                  | Parameter                                                | Conditions                                                        | Min                        | Тур     | Max       | Unit |

|-----------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------|----------------------------|---------|-----------|------|

| <b>CAN timing</b>                       | characteristics acc                                      | ording to ISO 11898-2:2024; see                                   | Figure                     | 7-1 and | d Figure  | 7-3  |

| $t_{D(TXDL-RXDL)}$                      | Delay time from TXD LOW to RXD LOW                       | STB = 0 V                                                         |                            |         | 255       | ns   |

| $t_{D(TXDH-RXDH)}$                      | Delay time from TXD HIGH to RXD HIGH                     | STB = 0 V                                                         |                            |         | 255       | ns   |

|                                         | characteristics acc<br>igure 7-3 and Figu                | ording to ISO 11898-2:2024; V <sub>C</sub> ore 7-5                | <sub>C</sub> = <b>4.75</b> | V to 5. | .25 V; se | ee   |

| t <sub>D(TXD-BUSDOM)</sub>              | Delay time from TXD to bus dominant                      | STB = 0 V                                                         |                            |         | 80        | ns   |

| t <sub>D(TXD-BUSREC)</sub>              | Delay time from TXD to bus recessive                     | STB = 0 V                                                         |                            |         | 80        | ns   |

| $t_{D(BUSDOM - RXD)}$                   | Delay time from<br>bus dominant to<br>RXD                | STB = 0 V                                                         |                            |         | 110       | ns   |

| t <sub>D(BUSREC -RXD)</sub>             | Delay time from<br>bus recessive to<br>RXD               | STB = 0 V                                                         |                            |         | 110       | ns   |

| $t_{D(TXDL-RXDL)}$                      | Delay time from<br>TXD LOW to<br>RXD LOW                 | STB = 0 V                                                         |                            |         | 190       | ns   |

| $t_{D(TXDH-RXDH)}$                      | Delay time from TXD HIGH to RXD HIGH                     | STB = 0 V                                                         |                            |         | 190       | ns   |

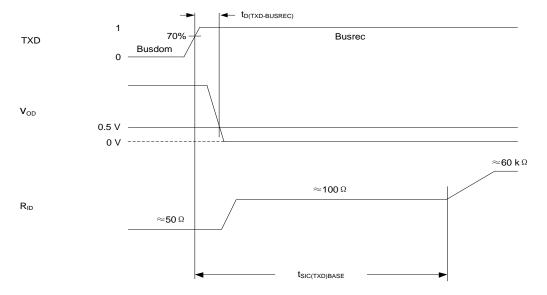

| t <sub>SIC(TXD)BASE</sub>               | delay time from<br>TXD to bus<br>active recessive<br>end | STB = 0 V (Note 1)                                                | 355                        |         | 480       | ns   |

|                                         |                                                          | according to ISO 11898-2:2024<br>4.75 V to 5.25 V; see Figure 7-1 |                            |         |           |      |

| $\Delta t_{BIT(BUS)}$                   | Transmitted recessive bit width deviation                | $\Delta t_{BIT(BUS)} = t_{BIT(BUS)} - t_{BIT(TXD)}$               | -10                        |         | 10        | ns   |

| $\Delta t_{ m REC}$                     | Receiver timing symmetry                                 | $\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$                    | -20                        |         | 15        | ns   |

| $\Delta t_{\mathrm{BIT}(\mathrm{RXD})}$ | Received recessive bit width deviation                   | $\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(TXD)}$                    | -30                        |         | 20        | ns   |

6.4 Electrical Characteristics (Dynamic) ---continued (Note 7)  $T_J$  = -40°C to +150°C;  $V_{CC}$  = 4.5V to 5.5V;  $V_{IO}$  = 2.9V to 5.5V;  $R_L$  = 60 $\Omega$ ;  $C_L$  = 100pF unless otherwise specified; all voltages are defined with respect to ground.

| Symbol                                    | Parameter                                         | Conditions                                                                                          | Min       | Тур   | Max      | Unit              |

|-------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|-------|----------|-------------------|

|                                           | _                                                 | s according to ISO 11898-2:2016<br>7-1 and Figure 7-3                                               | and ISC   | 11898 | 3-2:2024 | ; V <sub>CC</sub> |

| 4                                         | Transmitted                                       | 2 Mbit/s ( $t_{BIT(TXD)} = 500 \text{ ns}$ )                                                        | 490       |       | 510      | ns                |

| t <sub>BIT(BUS)</sub> recessive bit width |                                                   | 5 Mbit/s ( $t_{BIT(TXD)} = 200 \text{ ns}$ )                                                        | 190       |       | 210      | ns                |

| +                                         | Bit time on pin                                   | 2 Mbit/s ( $t_{BIT(TXD)} = 500 \text{ ns}$ )                                                        | 470       |       | 520      | ns                |

| $t_{BIT(RXD)}$                            | RXD (Note 1)                                      | 5 Mbit/s ( $t_{BIT(TXD)} = 200 \text{ ns}$ )                                                        | 170       |       | 220      | ns                |

| $\Delta t_{BIT(BUS)}$                     | Transmitted recessive bit width deviation         | 2 Mbit/s ( $t_{BIT(TXD)} = 500 \text{ ns}$ )<br>$\Delta t_{BIT(BUS)} = t_{BIT(BUS)} - t_{BIT(TXD)}$ | -65       |       | 30       | ns                |

| $\Delta t_{ m REC}$                       | Receiver timing symmetry                          | 2 Mbit/s ( $t_{BIT(TXD)} = 500 \text{ ns}$ )<br>$\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$      | -65       |       | 40       | ns                |

| $\Delta t_{BIT(RXD)}$                     | Received recessive bit width deviation            | 2 Mbit/s ( $t_{BIT(TXD)} = 500 \text{ ns}$ )<br>$\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(TXD)}$      | -100      |       | 50       | ns                |

| $\Delta t_{BIT(BUS)}$                     | Transmitted recessive bit width deviation         | 5 Mbit/s ( $t_{BIT(TXD)} = 200 \text{ ns}$ )<br>$\Delta t_{BIT(BUS)} = t_{BIT(BUS)} - t_{BIT(TXD)}$ | -45       |       | 10       | ns                |

| $\Delta t_{REC}$                          | Receiver timing symmetry                          | 5 Mbit/s ( $t_{BIT(TXD)} = 200 \text{ ns}$ )<br>$\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$      | -45       |       | 15       | ns                |

| $\Delta t_{BIT(RXD)}$                     | Received recessive bit width deviation            | 5 Mbit/s ( $t_{BIT(TXD)} = 200 \text{ ns}$ )<br>$\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(TXD)}$      | -80       |       | 20       | ns                |

| Dominant ti                               | me-out time; pin T                                | XD; (Note 3)                                                                                        |           |       |          |                   |

| $t_{TO(DOM)TXD}$                          | TXD dominant time-out time                        | STB = 0 V; TXD = 0V                                                                                 | 0.8       |       | 9        | ms                |

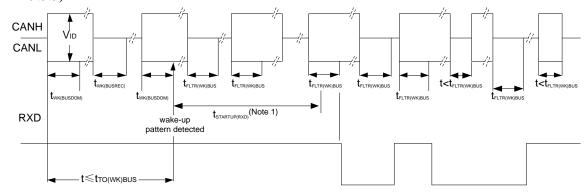

| Bus wake-up                               | times; pins CAN                                   | H and CANL; see Figure 9-3; (N                                                                      | ote 3, 4) |       |          |                   |

| $t_{WK(BUSDOM)}$                          | Bus dominant wake-up time                         | $STB = V_{\rm IO}$                                                                                  | 0.5       |       | 1.8      | us                |

| $t_{WK(BUSREC)} \\$                       | Bus recessive wake-up time                        | $STB = V_{IO}$                                                                                      | 0.5       |       | 1.8      | us                |

| t <sub>TO(WK)BUS</sub>                    | Bus wake-up time-out time                         | $STB = V_{IO}$                                                                                      | 0.8       |       | 9        | ms                |

| t <sub>FLTR(WK)BUS</sub>                  | Bus wake-up filter time                           | $STB = V_{IO}$                                                                                      |           |       | 1.8      | us                |

| Mode transi                               | _                                                 | 1                                                                                                   | 1         |       | 1        | 1                 |

| $t_{D(STB\text{-}NRM)}$                   | Mode change<br>time, from<br>standby to<br>normal |                                                                                                     |           |       | 50       | us                |

| t <sub>STARTUP(RXD)</sub>                 | RXD start-up time                                 | After wake-up detected (Note 5)                                                                     | 4         |       | 20       | us                |

### 6.4 Electrical Characteristics (Dynamic) --- continued (Note 7)

$T_J$  = -40°C to +150°C;  $V_{CC}$  = 4.5V to 5.5V;  $V_{IO}$  = 2.9V to 5.5V;  $R_L$  = 60 $\Omega$ ;  $C_L$  = 100pF unless otherwise specified; all voltages are defined with respect to ground.

| Symbol                | Parameter      | Conditions |   | Тур | Max | Unit |

|-----------------------|----------------|------------|---|-----|-----|------|

| IO filter; pin        | STB; (Note 6)  |            |   |     |     |      |

| t <sub>FLTR(IO)</sub> | IO filter time | on pin STB | 1 |     | 5   | us   |

Note 1: Not tested in production; guaranteed by design.

Note 2: Compliance with parameter set C requirements implies compliance for parameter sets A  $(t_{BIT(TXD)}) \ge 500$  ns, up to 2 Mbit/s) and B  $(t_{BIT(TXD)}) \ge 200$  ns, up to 5 Mbit/s).

Note 3: Time-out occurs between the min and max values. Time-out is guaranteed not to occur below the min value; time-out is guaranteed to occur above the max value.

Note 4: A dominant/recessive phase shorter than the min value is guaranteed not be seen as a dominant/recessive bit; a dominant/recessive phase longer than the max value is guaranteed to be seen as a dominant/recessive bit.

Note 5: When a wake-up is detected, RXD start-up time is between the min and max values. RXD cannot be relied on below the min value; RXD can be relied on above the max value; see Figure 9-3.

Note 6: Pulses shorter than the min value are guaranteed to be filtered out; pulses longer than the max value are guaranteed to be processed.

Note 7:  $V_{IO} = V_{CC}$  in non-VIO product variants.

### 7 Parameter Measurement Information

Figure 7-1. CAN transceiver timing test circuit

Figure 7-2. Test circuit for measuring transceiver transmitter driver symmetry

Figure 7-3. CAN transceiver timing diagram according to ISO 11898-2:2024

### 7 Parameter Measurement Information (continued)

Figure 7-4. CAN bus common-mode voltage according to SAE 1939-14

Figure 7-5. UMCAN1472 transmitter impedance and timing diagram for dominant-to-passive recessive transition

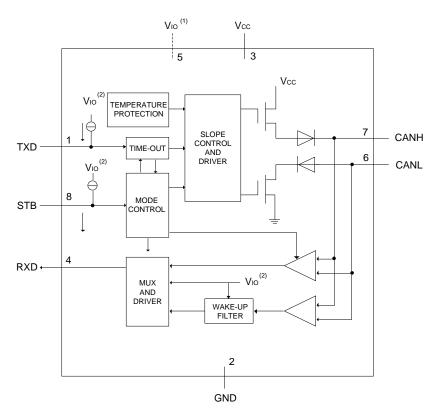

### 8 Block diagram

Figure 8-1. Block diagram

Note 1: Pin 5 is not connected in non-VIO product variants.

Note 2:  $V_{IO} = V_{CC}$  in non-VIO product variants.

### 9 Detailed Description

### 9.1 Operating modes

The UMCAN1472 supports three operating modes, Normal, Standby and Off. The operating mode is selected via pin STB. See Table for a description of the operating modes under normal supply conditions.

| 37.1    | Inputs  |           | Outputs          |                                                                          |  |

|---------|---------|-----------|------------------|--------------------------------------------------------------------------|--|

| Mode    | Pin STB | Pin TXD   | CAN driver       | Pin RXD                                                                  |  |

|         |         | LOW       | dominant         | LOW                                                                      |  |

| Normal  | LOW     | HIGH      | recessive        | LOW when bus dominant HIGH when bus recessive                            |  |

| Standby | HIGH    | x (Note1) | biased to ground | follows BUS when<br>wake-up detected<br>HIGH when no wake-up<br>detected |  |

| Off     | Х       | Х         | High-Z state     | High-Z state                                                             |  |

Note1: x' = don't care.

#### 9.1.1 Normal mode

A LOW level on pin STB selects Normal mode, provided the supply voltage on pin  $V_{CC}$  is above the standby undervoltage detection threshold,  $V_{UVD(STB)(VCC)}$ . Additionally, for the UMCAN1472V variant,  $V_{IO}$  must be above the switch-off undervoltage detection threshold  $V_{UVD(SWOFF)VIO}$ .

In this mode, the transceiver can transmit and receive data via the bus lines CANH and CANL (see Figure 8-1 for the block diagram). The differential receiver converts the analog data on the bus lines into digital data on pin RXD. The slopes of the output signals on the bus lines are controlled internally and are optimized in a way that guarantees the lowest possible EME. In order to support high bit rates, especially in CAN FD systems, the Signal Improvement function largely eliminates topology-related reflections and impedance mismatches. In recessive state, the output voltage on the bus pins is  $V_{\rm CC}/2$ .

#### 9.1.2 Standby mode

A HIGH level on pin STB selects Standby mode. In Standby mode, the transceiver is not able to transmit or correctly receive data via the bus lines. The transmitter and Normal mode receiver blocks are switched off to reduce supply current, and only a low-power differential receiver monitors the bus lines for activity. In Standby mode, the bus lines are biased to ground to minimize system supply current. The low-power receiver is supplied from  $V_{IO}$  and can detect CAN bus activity even if  $V_{IO}$  is the only available supply voltage. Pin RXD follows the bus after a wake-up request has been detected. A transition to Normal mode is triggered when STB is forced LOW.

#### 9.1.3 Off mode

The UMCAN1472 switches to Off mode from any mode when the supply voltage (on pin  $V_{IO}$  in UMCAN1472V and  $V_{CC}$  in UMCAN1472N) falls below the switch-off undervoltage threshold ( $V_{UVD(SWOFF)VIO}$  or  $V_{UVD(SWOFF)VCC}$ ). This is the default mode when the supply is first connected. In Off mode, the CAN pins and pin RXD are in a High-Z state.

#### 9.1.4 Operating modes and gap-free operation

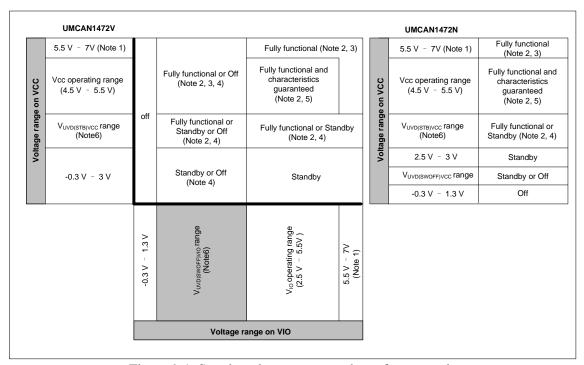

Gap-free operation guarantees defined behavior at all voltage levels. Supply voltage-to-operating mode mapping is detailed in Figure 9-1.

Figure 9-1. Supply voltage ranges and gap-free operation

- Note 1: Maximum voltage should never exceed 7 V.

- Note 2: Target transceiver functionality as described in this datasheet is applicable.

- Note 3: Prolonged operation of the device outside the operating range may impact reliability over lifetime. Returning to the operating range, datasheet characteristics are guaranteed provided the AMR has not been exceeded.

- Note 4: For a given value of  $V_{IO}$ , a specific device will be in a single defined state determined by its undervoltage detection thresholds ( $V_{UVD(STB)VCC}$  and  $V_{UVD(SWOFF)VIO}$ ). The actual thresholds can vary between devices (within the ranges specified in this datasheet). To guarantee the device will be in a specific state,  $V_{IO}$  and  $V_{CC}$  must be either above the maximum or below the minimum thresholds specified for these undervoltage detection ranges.

- Note 5: Datasheet characteristics are guaranteed within the  $V_{\text{CC}}$  and  $V_{\text{IO}}$  operating ranges. Exceptions are described in the Static and Dynamic characteristics tables.

- Note 6: The following applies to UMCAN1472:

- If both  $V_{CC}$  and  $V_{IO}$  are above the undervoltage threshold, the device is fully functional.

- If V<sub>CC</sub> is below and V<sub>IO</sub> above the undervoltage threshold, the device is in Standby mode.

- If  $V_{IO}$  is below the undervoltage threshold, the device is in Off mode, regardless of  $V_{CC}$ .

#### 9.2 Remote wake-up (via the CAN bus)

The UMCAN1472 wakes up from Standby mode when a dedicated wake-up pattern (specified in ISO 11898-2:2024) is detected on the bus. This filtering helps avoid spurious wake-up events. A spurious wake-up sequence could be triggered by, for example, a dominant clamped bus or by dominant phases due to noise or spikes on the bus.

The wake-up pattern consists of:

- a dominant phase of at least twk(BUSDOM) followed by

- a recessive phase of at least t<sub>WK(BUSREC)</sub> followed by

- a dominant phase of at least twk(BUSDOM)

Dominant or recessive bits between the above mentioned phases that are shorter than  $t_{WK(BUSDOM)}$  and  $t_{WK(BUSREC)}$  respectively are ignored.

The complete dominant-recessive-dominant pattern must be received within  $t_{TO(WK)BUS}$  to be recognized as a valid wake-up pattern. Otherwise, the internal wake-up logic is reset. The complete wake-up pattern will then need to be retransmitted to trigger a wake-up event. Pin RXD remains HIGH until the wake-up event has been triggered.

After a wake-up sequence has been detected, the UMCAN1472 will remain in Standby mode with the bus signals reflected on RXD after t<sub>STARTUP(RXD)</sub>. Note that dominant or recessive phases lasting less than t<sub>FLTR(WK)BUS</sub> will not be detected by the low-power differential receiver and will not be reflected on RXD in Standby mode.

A wake-up event is not flagged on RXD if any of the following events occurs while a valid wake-up pattern is being received:

- The device switches to Normal mode

- The complete wake-up pattern was not received within t<sub>TO(WK)BUS</sub>

- A  $V_{CC}$  or  $V_{IO}$  undervoltage is detected ( $V_{CC} < V_{UVD(SWOFF)VCC}$  or  $V_{IO} < V_{UVD(SWOFF)VIO}$ ; see 9.3.3)

Figure 9-1. Wake-up Timing

Note 1: During  $t_{STARTUP(RXD)}$ , the low-power receiver is on but pin RXD is not active (i.e. HIGH/recessive). The first dominant pulse of width  $\geq t_{FLTR(WK)BUS}$  that ends after  $t_{STARTUP(RXD)}$  will trigger RXD to go LOW/dominant.

#### 9.3 Fail-safe features

#### 9.3.1 TXD dominant time-out function

A 'TXD dominant time-out' timer is started when pin TXD is set LOW. If the LOW state on this pin persists for longer than  $t_{TO(DOM)TXD}$ , the transmitter is disabled, releasing the bus lines to recessive state. This function prevents a hardware and/or software application failure from driving the bus lines to a permanent dominant state (blocking all network communications). The TXD dominant time-out timer is reset when pin TXD is set HIGH.

#### 9.3.2 Internal biasing of TXD and STB input pins

Pins TXD and STB have internal pull-ups to  $V_{CC}$  ( $V_{IO}$  for variants with a  $V_{IO}$  pin) to ensure a safe, defined state in case one or both of these pins are left floating. Pull-up currents flow in these pins in all states; both pins should be held HIGH in Standby mode to minimize supply current.

#### 9.3.3 Undervoltage detection on pins $V_{CC}$ and $V_{IO}$

If  $V_{CC}$  drops below the standby undervoltage detection level,  $V_{UVD(STB)VCC}$ , the transceiver switches to Standby mode. The logic state of pin STB is ignored until  $V_{CC}$  has recovered.

In versions with a  $V_{IO}$  pin, if  $V_{IO}$  drops below the switch-off undervoltage detection level ( $V_{UVD(SWOFF)VIO}$ ), the transceiver switches off and disengages from the bus (High-Z) until  $V_{IO}$  has recovered.

In versions without a  $V_{IO}$  pin, if  $V_{CC}$  drops below the switch-off undervoltage detection level ( $V_{UVD(SWOFF)VCC}$ ), the transceiver switches off and disengages from the bus (High-Z) until  $V_{CC}$  has recovered.

#### 9.3.4 Overtemperature protection

The output drivers are protected against overtemperature conditions. If the virtual junction temperature exceeds the shutdown junction temperature,  $T_{J(SD)}$ , both output drivers are disabled. When the virtual junction temperature drops below  $T_{J(SD)}$  again, the output drivers recover once TXD has been reset to HIGH. Including the TXD condition prevents output driver oscillation due to small variations in temperature.

#### 9.3.5 VIO supply pin (UMCAN1472VS8 and UMCAN1472VDA variants)

Pin  $V_{IO}$  should be connected to the microcontroller supply voltage. This will adjust the signal levels of pins TXD, RXD and STB to the I/O levels of the microcontroller. Pin  $V_{IO}$  also provides the internal supply voltage for the low-power differential receiver in the transceiver. For applications running in low-power mode, this allows the bus lines to be monitored for activity even if there is no supply voltage on pin  $V_{CC}$ .

For variants of the UMCAN1472 without a  $V_{IO}$  pin, all circuitry is connected to  $V_{CC}$  (pin 5 is not bonded). The signal levels of pins TXD, RXD and STB are then compatible with 5 V microcontrollers. This allows the device to interface with both 3.3 V and 5 V-supplied microcontrollers, provided the microcontroller I/Os are 5 V tolerant.

### 9.4 Signal Improvement

Signal improvement is an additional capability added to CAN FD transceiver that enhances the maximum data rate achievable in complex star topologies by minimizing signal ringing. Signal ringing is the result of reflections caused by impedance mismatch at various points in a CAN network due to the nodes that act as stubs.

Recessive-to-dominant signal edge is usually clean as it is strongly driven by the transmitter. Transmitter output impedance of CAN transceiver is  $\approx 50~\Omega$  and matches to the network characteristic impedance. For a regular CAN FD transceiver, dominant-to-recessive edge is when the driver output impedance goes to  $\approx 60~k\Omega$  and signal reflected back experiences impedance mismatch which causes ringing. UMCAN1472 resolves this issue by TX-based Signal improvement capability (SIC). The device continues to drive the bus recessive until  $t_{\rm SIC(TXD)BASE}$  so that reflections die down and recessive bit is clean at sampling point. In the active recessive phase, transmitter output impedance is low ( $\approx 100~\Omega$ ). After this phase is over and device goes to passive recessive phase, driver output impedance goes to high-Z. This phenomenon is explained at Figure 7-5.

# **Package Information**

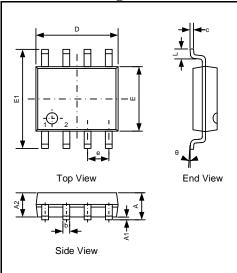

### SOP8

**Outline Drawing**

| DIMENSIONS |             |      |      |           |       |       |  |

|------------|-------------|------|------|-----------|-------|-------|--|

| Symbol     | MILLIMETERS |      |      | INCHES    |       |       |  |

|            | Min         | Тур  | Max  | Min       | Тур   | Max   |  |

| A          | 1.35        | 1.55 | 1.75 | 0.053     | 0.061 | 0.069 |  |

| A1         | 0.10        | -    | 0.25 | 0.004     | -     | 0.010 |  |

| A2         | 1.25        | -    | 1.65 | 0.049     | -     | 0.065 |  |

| b          | 0.30        | -    | 0.51 | 0.012     | -     | 0.020 |  |

| c          | 0.15        | -    | 0.25 | 0.006     | -     | 0.010 |  |

| D          | 4.70        | 4.90 | 5.10 | 0.185     | 0.193 | 0.200 |  |

| Е          | 3.80        | 3.90 | 4.00 | 0.150     | 0.154 | 0.157 |  |

| E1         | 5.80        | 6.00 | 6.20 | 0.228     | 0.236 | 0.244 |  |

| e          | 1.27BSC     |      |      | 0.050 BSC |       |       |  |

| L          | 0.40        |      | 1.27 | 0.015     | _     | 0.050 |  |

| θ          | 0°          | -    | 8°   | 0 °       | -     | 8°    |  |

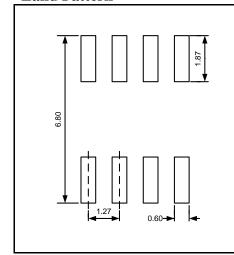

### **Land Pattern**

### NOTES:

- 1. Compound dimension: 4.90×3.90;

- 2. Unit: mm;

- 3. General tolerance  $\pm 0.05$ mm unless otherwise specified;

- 4. The layout is just for reference.

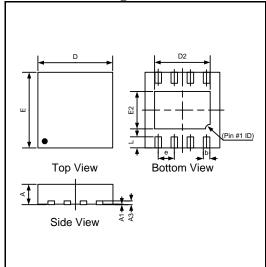

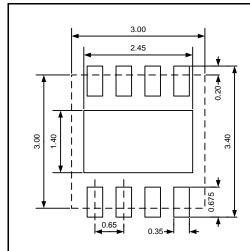

### **DFN8 3.0×3.0**

## **Outline Drawing**

| DIMENSIONS |             |      |      |          |       |       |  |

|------------|-------------|------|------|----------|-------|-------|--|

| Symbol     | MILLIMETERS |      |      | INCHES   |       |       |  |

|            | Min         | Тур  | Max  | Min      | Тур   | Max   |  |

| A          | 0.57        | -    | 0.80 | 0.022    | -     | 0.031 |  |

| A1         | 0.00        | -    | 0.05 | 0.000    | -     | 0.002 |  |

| A3         | 0.20REF     |      |      | 0.008REF |       |       |  |

| b          | 0.20        | -    | 0.35 | 0.008    | -     | 0.014 |  |

| D          | 2.90        | 3.00 | 3.10 | 0.114    | 0.118 | 0.122 |  |

| D2         | 2.15        | -    | 2.55 | 0.085    | -     | 0.100 |  |

| Е          | 2.90        | 3.00 | 3.10 | 0.114    | 0.118 | 0.122 |  |

| E2         | 1.40        | -    | 1.75 | 0.055    | -     | 0.069 |  |

| e          | 0.65BSC     |      |      | 0.026BSC |       |       |  |

| L          | 0.30        | -    | 0.60 | 0.012    | -     | 0.024 |  |

### **Land Pattern**

### NOTES:

- 1. Compound dimension: 3.00×3.00;

- 2. Unit: mm;

- 3. General tolerance ±0.05mm unless otherwise specified;

- 4. The layout is just for reference.

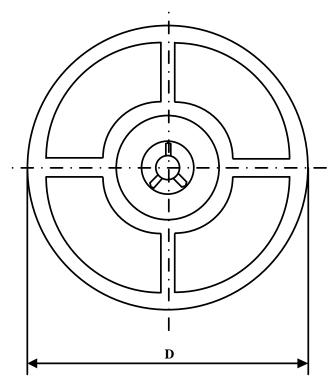

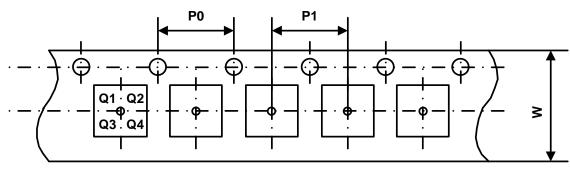

# **Packing Information**

| Part Number  | Package Type | Carrier<br>Width<br>(W) | Pitch<br>(P0) | Pitch<br>(P1) | Reel Size<br>(D) | PIN 1<br>Quadrant |

|--------------|--------------|-------------------------|---------------|---------------|------------------|-------------------|

| UMCAN1472VS8 | SOP8         | 12 mm                   | 4 mm          | 8 mm          | 330 mm           | Q1                |

| UMCAN1472VDA | DFN8 3.0×3.0 | 12 mm                   | 4 mm          | 8 mm          | 330 mm           | Q1                |

| UMCAN1472NS8 | SOP8         | 12 mm                   | 4 mm          | 8 mm          | 330 mm           | Q1                |

| UMCAN1472NDA | DFN8 3.0×3.0 | 12 mm                   | 4 mm          | 8 mm          | 330 mm           | Q1                |

#### **GREEN COMPLIANCE**

Union Semiconductor is committed to environmental excellence in all aspects of its operations including meeting or exceeding regulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.

All Union components are compliant with the RoHS directive, which helps to support customers in their compliance with environmental directives. For more green compliance information, please visit:

http://www.union-ic.com/index.aspx?cat code=RoHSDeclaration

#### IMPORTANT NOTICE

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Union assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. Union reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.